# Taming Model Incongruities in Networked Systems

**Niray Atre**

CMU-CS-25-140 September 2025

Computer Science Department School of Computer Science Carnegie Mellon University Pittsburgh, PA 15213

#### **Thesis Committee:**

Justine Sherry (Chair)

Vyas Sekar

Weina Wang

Brighten Godfrey (UIUC)

Submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy.

Copyright © 2025 Nirav Atre

This research was funded by National Science Foundation (NSF) Awards 1700521 and 2007733, the CONIX Research Center (one of six centers in JUMP, a Semiconductor Research Corporation program sponsored by DARPA), Intel and VMware through the Intel/VMware Crossroads 3D-FPGA Academic Research Center, a VMWare Systems Research Award, a Cylab Presidential Fellowship, and a Google Research Gift.

For my father, Rajesh Atre, who taught me to pour everything I have into anything I do; and my mother, Vasundhra Atre, from whom I learned that when something is necessary, it cannot be impossible.

#### **Abstract**

We reason about computer systems via models of their behavior — whether implicit *mental* models, or explicit *mathematical* models. These models are the linchpins of our decision-making ability, *e.g.*, in formulating service-level agreements (SLAs), or tendering performance claims. Unfortunately, a growing disconnect between how systems are modeled and how they are actually deployed has engendered a class of problems that we call **model incongruity**: circumstances where a model's prediction deviates significantly from real-world behavior. Model incongruities are highly pervasive in modern systems, resulting in expensive performance anomalies, scalability bottlenecks, and security vulnerabilities.

In this thesis, we argue that many incongruities observed in practice today are not a fundamental limitation of our modeling capabilities, but rather artifacts of using the *wrong* models. We show that: (a) assumptions centrally underpinning contemporary models of network subsystems have drifted far from deployment realities; (b) these assumptions are frequently violated in the field, subverting the operator's expectations about key metrics in highly unexpected ways; and, (c) making modest model refinements not only yields designs with state-of-the-art performance, attack resilience, and scalability, but also enables us to make rigorous mathematical guarantees about the resulting system's behavior.

We exemplify this point using case studies of three ubiquitous network subsystems. First, we will describe delayed hits, an incongruity arising in high-performance caching systems which breaks the textbook caching principle that maximizing cache hit-rate also minimizes latency, and causes every existing caching algorithm to make latency-suboptimal decisions; in this context, we will introduce Minimum-AggregateDelay (MAD), a turnkey augmentation to existing algorithms that makes them aware of delayed hits, yielding 5-35% lower request latencies. Second, we will describe algorithmic complexity attacks (ACAs), a highly potent class of Denial-of-Service attacks arising from transient workload incongruity; in this context, we will introduce SurgeProtector, an adversarial scheduling framework that provably protects network dataplanes against ACAs, resulting in 90-99% reduction in harm for the same volume of attack traffic. Finally, we will describe BBQ, a system borne out of addressing design incongruity in hardware packet schedulers. BBQ, for the first time, makes it *feasible* to deploy packet scheduling at line-rate on modern network switches and SmartNICs, bridging a long-standing gap between the concept and execution of programmable hardware packet scheduling.

### Acknowledgments

Anyone who had the misfortune of asking me "how I was doing" between 2018 and 2025 has likely endured my monologue on why life as a Ph.D. student is, in my opinion, the ideal state of being. I gave three arguments in support of this controversial claim: (1) one has infinite intellectual freedom coupled with little-to-no external accountability; (2) one gets paid every two weeks, no questions asked; and, (3) everyone answers one's emails (at least the first time). It took me several years to realize that these were not, in fact, universal features of a Ph.D. program, but rather almost purely a function of one's advisor. So, thank you, Justine, for your unwavering (often inexplicably so) faith in me, for shielding me from the riptides of academic bureaucracy, and for allowing me to spend freely the vast amount of goodwill and professional capital that you have so effortlessly cultivated over the years. You are the absolute best.

I owe an immense debt of gratitude to an incredible set of mentors, starting with my thesis committee: Weina Wang, Vyas Sekar, and Brighten Godfrey. Thank you, Weina, for taking me under your wing (despite my penchant for flipping inequalities), and for being such a gentle, patient, and magnanimous guide through the beautiful world of theory; I am (and always will) be delighted to be mistaken for your student. Thank you, Vyas, for being my North Star in uncertain times; your knack for casually dispensing life-changing and research-defining advice has kept me from going astray more times than I can count; to this day, I give floundering students the exact same advice I did 5 years ago: stop talking to me, and go find Vyas. Thank you, Brighten, for being so deeply invested and championing this work, and for your unwavering support throughout my job search (including entertaining my preposterously last-minute letter requests). I am also deeply grateful to Aditi Raghunathan, Anirudh Sivaraman, Anupam Gupta, Aurojit Panda, Balaji Prabhakar, Daniel Berger, Giulia Fanti, James Hoe, Jonathan Rose, Keith Winstein, Mahmoud Elhaddad, Mor Harchol-Balter, Nathan Beckmann, Nick McKeown, Peter Steenkiste, Phil Levis, Rashmi Vinayak, Riccardo Paccagnella, Roy Want, Ruben Martins, Srini Seshan, and Yuvraj Agarwal for their sage advice and generous mentorship through various pivotal moments in my academic career.

I started graduate school with the preconceived notion that the Ph.D. journey was a solitary one; thankfully, I was grossly mistaken. I am incredibly fortunate to have met some truly remarkable people who have made Pittsbugh feel like home, starting with Justine's extended research group and the SNAP Lab: Adithya Abraham Philip, Antonis Manousis, Anup Agarwal, Benjamin Carleton, Chris Canel, Erica Chiang, Francisco Pereira, Hugo Sadok (special thanks for being my closest collaborator, patiently listening to my unhinged rants about hardware synthesis tools, and tolerating 6 years' worth of questionable humor), Ioannis Anagnostides, Isabel Suizo, Kshitij Rana, Margarida Ferreira, Matt Butrovich, Miguel Ferreira, Ranysha Ware, Sagar Bharadwaj, Shawn Chen, Yiran Lei, Zhipeng Zhao, and Zili Meng.

Beyond my research group, I am fortunate to have met a truly wonderful set of souls in the broader CSD, CMU, UPitt, and academic communities. My housemates over the years: Abhiram Kothapalli, Ben Koby, Izzy Grosof, Pete Gungel, and Roger Iyengar. The brunch/tennis group: Adithya Pratapa, Aditi Kabra, Ankush Jain, Arjun Lakshmipathy, Jovina Vaswani, Mansi Goyal, Mara Aragones, Mihir Bala, Mugdha Deokar, Pratiksha Thaker, Sai Sandeep, Sakshi Satyanand, Sanjith Athlur, Shilpa Anna George, Sitoshna Jatty, and Surabhi Gupta. The best CSD cohort ever (plus honorary members): Arjun Teh, David Kahn, Giulio Zhou, Jalani Williams, Joshua Williams, Mark Gillespie, Mikhail (Misha) Khodak, Pallavi Koppol, Shir Maimon, and Siva Somayyajula. And dear friends I made through the most fortuitous of circumstances: Akshay Narayan, Ananya Joshi, Angela Jiang, Anuj Kalia, Carlos Martin, Daiyaan Arfeen, Deepanjali Mishra, Deepti Raghavan, Devdeep Ray, Dorian Chan, Francisco Maturana, Gabriele Farina, Gaurav Manek, Jack Kosaian, Jason Choi, Karan Ahuja, Long Pham, Pranav Khadpe, Prateesh Goyal, Rishabh Iyer, Sam Westrick, Sara McAllister, Siddharth Jayashankar, Sol Boucher, Venkat Arun, and Vibhaalakshmi Sivaraman. I am also grateful to the Parallel Data Lab (PDL) for broadening my horizons, both in terms of research, and social/industry connections.

After 7 years of scheduling conference rooms at the very last minute, requesting reimbursements several weeks past due, and scrambling for spare office keys, I am convinced beyond a shadow of doubt that CSD and PDL have *the best* administrative and support staff in existence. I am deeply grateful to Angy Malloy, Catherine Copetas, Deb Cavlovich, Emily Spencer, Joan Digney, Karen Lindenfelser, Matthew Stewart, Olivia Zane, and Sara Kuntz for all their help throughout the years. This place would not function without any one of you!

Finally, none of this would have been possible without my parents (Rajesh and Vasundhra Atre), and grandparents (Padmakar and Jayashree Atre, and Trilok and Kananbala Kohli), who have made ineffable sacrifices to get me here. This thesis is dedicated to them.

# **Contents**

| 1 | Intr | oduction                                                       | 1  |

|---|------|----------------------------------------------------------------|----|

|   | 1.1  | Why Now?                                                       | 3  |

|   | 1.2  | Summary of Results                                             | 4  |

|   | 1.3  | Thesis Organization                                            | 5  |

| 2 | Cac  | hing with Delayed Hits                                         | 7  |

|   | 2.1  | Incongruity in the Classical Model of Caching                  | 8  |

|   | 2.2  | Impact of Delayed Hits                                         | 0  |

|   |      | 2.2.1 Misleading Operators                                     | 0  |

|   |      | 2.2.2 Misleading Algorithms                                    | 2  |

|   | 2.3  | Latency Minimization in the Delayed Hits Model                 | 3  |

|   |      | 2.3.1 A Case for Principled Analysis                           | 3  |

|   |      | 2.3.2 Problem Formulation                                      | 4  |

|   | 2.4  | Belatedly: Offline, Latency-Optimal Caching                    | 6  |

|   |      | 2.4.1 Network Flow Formulation                                 | 7  |

|   |      | 2.4.2 Delayed Hits and Empirical Latencies                     | 0  |

|   |      | 2.4.3 Optimizations to Reduce Complexity                       | 2  |

|   |      | 2.4.4 Performance Evaluation                                   | 6  |

|   |      | 2.4.5 Proof of Optimality                                      | 7  |

|   | 2.5  | MAD: Online, Low-Latency Caching                               | 4  |

|   |      | 2.5.1 Proxy Oracle: Bélády-AggregateDelay                      | 5  |

|   |      | 2.5.2 Online Algorithm: MINIMUM-AGGREGATEDELAY (MAD)           | 6  |

|   | 2.6  | Evaluating MAD                                                 | 8  |

|   |      | 2.6.1 Experimental Setup                                       | 8  |

|   |      | 2.6.2 Prototype Evaluation on CDN Trace                        | 9  |

|   |      | 2.6.3 Simulation Results: Systems                              | :1 |

|   |      | 2.6.4 Simulation Results: Analysis                             | :3 |

|   | 2.7  | Related Work                                                   | :5 |

|   | 2.8  | Broader Impact, Open Questions, and Conclusion                 | :6 |

| 3 | Miti | igating Algorithmic Complexity Attacks on Network Subsystems 4 | 7  |

|   | 3.1  | Workload Incongruity                                           | 8  |

|   | 3.2  | Background and Motivation                                      | .9 |

|   |     | 3.2.1 High Pervasiveness and Potency of ACAs         |

|---|-----|------------------------------------------------------|

|   |     | 3.2.2 Existing Defenses are Insufficient             |

|   | 3.3 | Incongruity-Aware Workload Model                     |

|   |     | 3.3.1 System Model                                   |

|   |     | 3.3.2 Threat Model                                   |

|   |     | 3.3.3 Quantifying Vulnerability                      |

|   | 3.4 | Mitigating ACAs using Scheduling                     |

|   |     | 3.4.1 First-Come First-Serve (FCFS)                  |

|   |     | 3.4.2 Fair Queueing (FQ)                             |

|   |     | 3.4.3 Shortest Job First (SJF)                       |

|   |     | 3.4.4 Weighted Shortest Job First (WSJF)             |

|   | 3.5 | SURGEPROTECTOR Implementation                        |

|   |     | 3.5.1 Overview of Vulnerable Components              |

|   |     | 3.5.2 Predicting Job Sizes                           |

|   |     | 3.5.3 Keeping (TCP) Flows In-Order                   |

|   |     | 3.5.4 Designing Adversary-Proof Schedulers           |

|   | 3.6 | Evaluation                                           |

|   |     | 3.6.1 SurgeProtector + Pigasus                       |

|   |     | 3.6.2 SurgeProtector in Simulation                   |

|   |     | 3.6.3 SurgeProtector Scheduler                       |

|   | 3.7 | Limitations and Open Questions                       |

|   | 3.8 | Related Work                                         |

|   | 3.9 | Conclusion                                           |

|   | _   |                                                      |

| 4 | _   | loyable Hardware Packet Scheduling 79                |

|   | 4.1 | Background and Motivation                            |

|   |     | 4.1.1 Design Incongruity                             |

|   | 4.0 | 4.1.2 Exploring a Different Tradeoff                 |

|   | 4.2 | BBQ Overview                                         |

|   |     | 4.2.1 Data Structure                                 |

|   |     | 4.2.2 BBQ Primitive                                  |

|   |     | 4.2.3 Goals and Challenges                           |

|   | 4.3 | BBQ Architecture                                     |

|   |     | 4.3.1 Hardware Pipeline                              |

|   |     | 4.3.2 A Fully-Pipelined Architecture                 |

|   |     | 4.3.3 Implementing Subtree Occupancy Counters (StOC) |

|   | 4.4 | Logical Partitioning in Practice                     |

|   |     | 4.4.1 Existing Designs                               |

|   |     | 4.4.2 Logical Partitioning in BBQ                    |

|   | 4.5 | Extensions to the BBQ Primitive                      |

|   |     | 4.5.1 BBQ : A Latency-Free BBQ                       |

|   |     | 4.5.2 Dynamic Priority Ranges                        |

|   | 4.6 | Evaluation                                           |

|   |     | 4.6.1 Setup and Methodology                          |

| Bi | ibliography 115 |         |        |       |      |       |      |     |            |     |    |     |     |   |   |   |   |   |   |   |      |   |   |   |   |         |

|----|-----------------|---------|--------|-------|------|-------|------|-----|------------|-----|----|-----|-----|---|---|---|---|---|---|---|------|---|---|---|---|---------|

| 5  | Con             | clusion | 1      |       |      |       |      |     |            |     |    |     |     |   |   |   |   |   |   |   |      |   |   |   |   | 113     |

|    | 4.10            | Conclu  | usion  |       |      |       |      |     |            |     | •  |     |     |   | • | • | • | • | • | • | <br> | • | • | • | • | <br>111 |

|    | 4.9             | Related |        |       |      |       |      |     |            |     |    |     |     |   |   |   |   |   |   |   |      |   |   |   |   |         |

|    | 4.8             | Limita  | tions  | and   | Ope  | n Qı  | ıest | ion | <b>S</b> . |     |    |     |     |   |   |   |   |   |   |   | <br> |   |   |   |   | <br>109 |

|    |                 | 4.7.2   | Pacl   | cet S | chec | lulin | ıg o | n C | lou        | d S | ma | rtl | NIC | s |   |   |   |   |   |   | <br> |   |   |   |   | <br>108 |

|    |                 | 4.7.1   | Pacl   | cet S | chec | lulin | ıg o | n S | wit        | che | S  |     |     |   |   |   |   |   |   |   | <br> |   |   |   |   | <br>108 |

|    | 4.7             | Applic  | cation | s     |      |       |      |     |            |     |    |     |     |   |   |   |   |   |   |   | <br> |   |   |   |   | <br>108 |

|    |                 | 4.6.3   | ASI    | С.,   |      |       |      |     |            |     |    |     |     |   |   |   |   |   |   |   | <br> |   |   |   |   | <br>107 |

|    |                 |         | FPG    |       |      |       |      |     |            |     |    |     |     |   |   |   |   |   |   |   |      |   |   |   |   |         |

# **List of Figures**

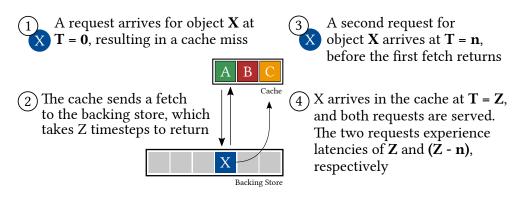

| 2.1  | Two requests for object X arrive within $Z$ timesteps of each other                          | 8  |

|------|----------------------------------------------------------------------------------------------|----|

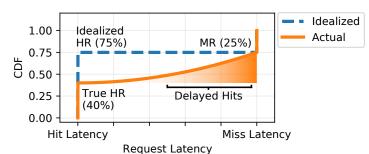

| 2.2  | Example cumulative density function (CDF) of request latencies. Delayed hits                 |    |

|      | account for the gap between the <i>true</i> hit-rate (HR) and the miss-rate (MR)             | 9  |

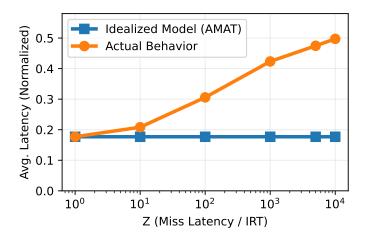

| 2.3  | Normalized latency predictions with (Actual) and without (Idealized) account-                |    |

|      | ing for delayed hits                                                                         | 11 |

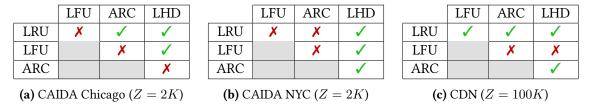

| 2.4  | Pairwise comparisons between four online caching algorithms                                  | 11 |

| 2.5  | For the given trace, with a cache of size 2 and a $\mathbb Z$ value of 3, Bélády's algorithm |    |

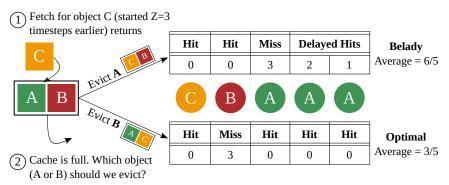

|      | chooses a latency-suboptimal schedule                                                        | 12 |

| 2.6  | The BELATEDLY pipeline for computing bounds on latency-optimal cache sched-                  |    |

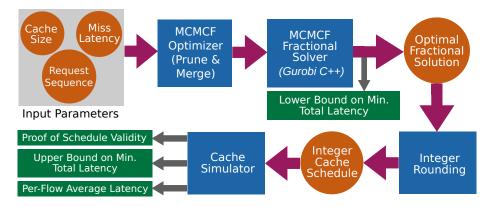

|      | ule using MCMCF reduction                                                                    | 16 |

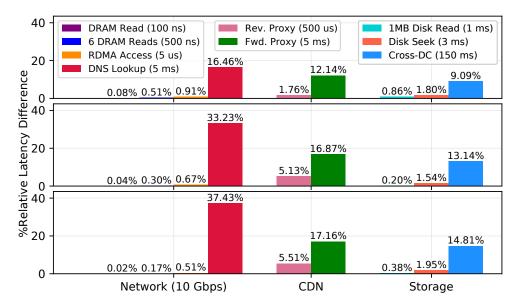

| 2.7  | Latency gap between Bélády and BELATEDLY for different application scenarios                 |    |

|      | (Network, CDN, Storage) today. Top to bottom: 1%, 5%, and 10% cache sizes                    | 21 |

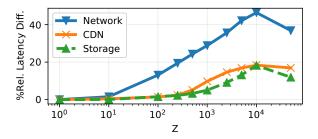

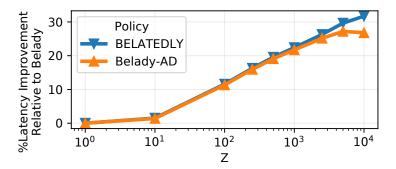

| 2.8  | %Relative latency difference between Bélády and Belatedly as a function of $Z$ .             |    |

|      | Using cache size, $c=5\%$ (expressed as a percentage of the maximum number                   |    |

|      | of concurrent flows).                                                                        | 21 |

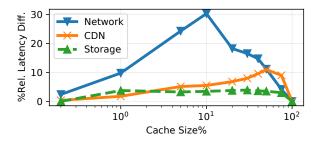

| 2.9  | %Relative latency difference between Bélády and BELATEDLY as a function of                   |    |

|      | cache size. Using $Z=500.$                                                                   | 21 |

| 2.10 | Relative latency improvement <i>vs</i> burstiness (for Network traffic). Bursty flows        |    |

|      | suffer less under Belatedly                                                                  | 22 |

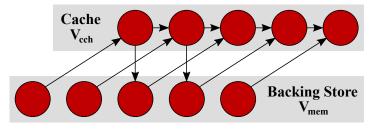

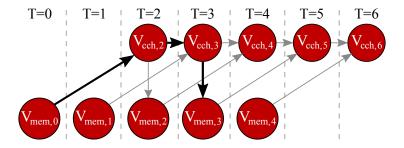

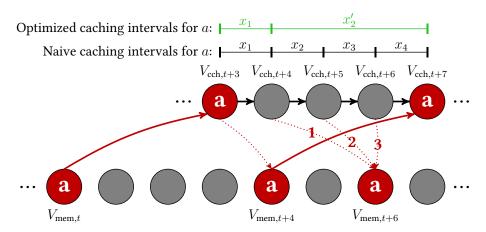

| 2.11 | A fragment of a request sequence highlighting nodes and edges corresponding                  |    |

|      | to object $a$ (colored red), with $Z = 3$                                                    | 23 |

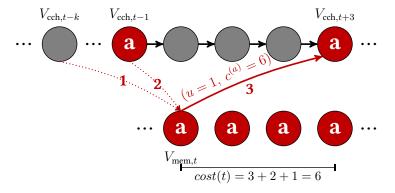

| 2.12 | A fragment of a request sequence highlighting ingress and egress edges for node              |    |

|      | $V_{\text{mem},t}$ , with $Z=3$                                                              | 24 |

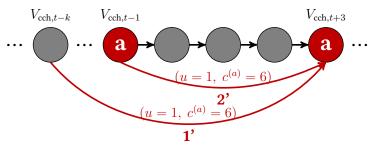

| 2.13 | The optimized representation with backing store nodes removed                                | 25 |

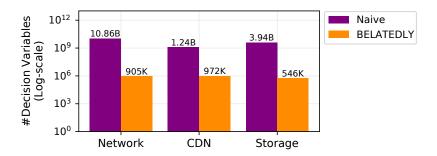

| 2.14 | Number of decision variables in the naive MCMCF formulation versus BELAT-                    |    |

|      | EDLY for different application scenarios                                                     | 26 |

| 2.15 | Ranking objects solely based on aggregate delay may lead to poor utilization of              |    |

|      | cache space.                                                                                 | 35 |

| 2.16 | BÉLÁDY-AD closely trails belatedly                                                           | 36 |

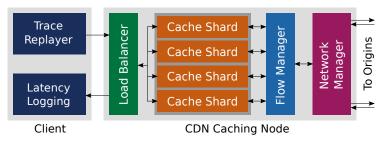

| 2.17 | Architecture of our experimental prototype                                                   | 38 |

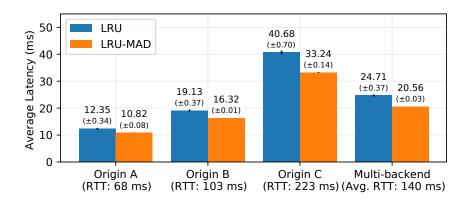

| 2.18 | Prototype results for different origin locations                                             | 39 |

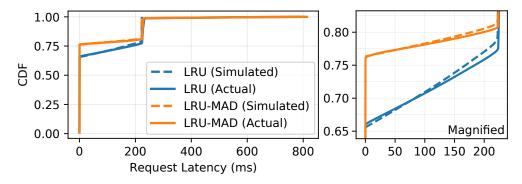

| 2.19 | CDF of latencies in simulation versus real experiments                                       | 40 |

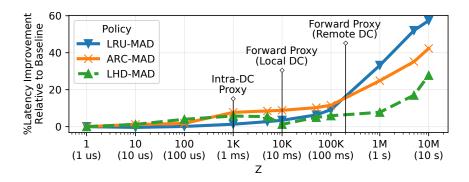

| 2.20 | MAD simulations for the CDN Trace                                                            | 41 |

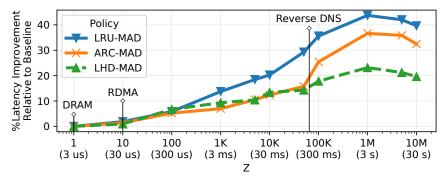

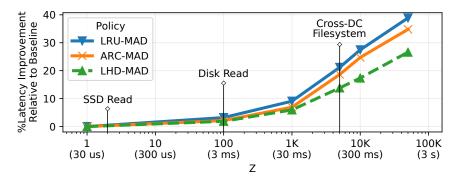

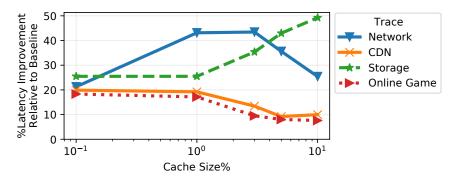

|      | MAD simulations for the Network Trace                                                                                                                                                                                                                                                          | 42<br>42 |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 2.23 | Relative latency difference between LRU-MAD and LRU as a function of the                                                                                                                                                                                                                       | 42       |

| 2.23 | cache size. Using $Z = 100K$                                                                                                                                                                                                                                                                   | 43       |

| 2.24 | Like Belatedly, MAD prioritizes bursty objects                                                                                                                                                                                                                                                 | 44       |

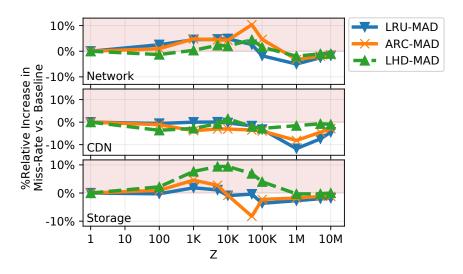

| 2.25 | Percent relative change in miss-rate between MAD and various baseline caching algorithms for Network, CDN, and Storage                                                                                                                                                                         | 44       |

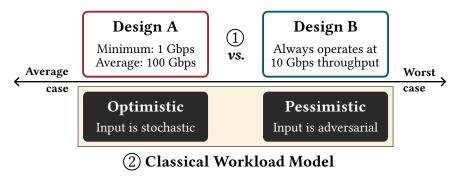

| 3.1  | The classical model posits a false dichotomy between workload characteristics.                                                                                                                                                                                                                 | 48       |

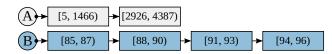

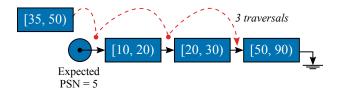

| 3.2  | TCP reassembly implemented using a linked list [162]. Each node in the list represents a range of packet sequence numbers.                                                                                                                                                                     | 50       |

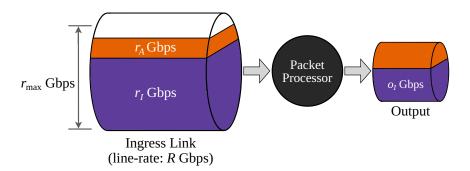

| 3.3  | Refined model treating the workload as a superposition of <i>purely stochastic</i> in-                                                                                                                                                                                                         | 30       |

|      | nocent traffic (purple) and a sliver of <i>adversarial</i> traffic (orange)                                                                                                                                                                                                                    | 52       |

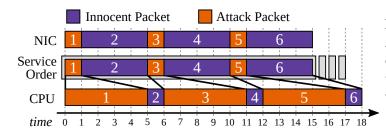

| 3.4  | FCFS fails to protect against ACAs. Using minimum-sized packets encoding maximum-sized jobs allows the attacker to induce significant amounts of work                                                                                                                                          |          |

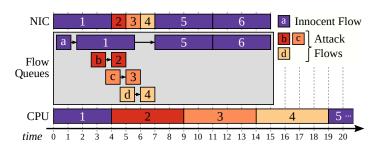

| 3.5  | in the system                                                                                                                                                                                                                                                                                  | 55       |

| 5.5  | attacker can trick the FQ scheduler into giving them a large fraction of service time using multiple flows. In steady-state, the attacker receives 75% of the total                                                                                                                            |          |

| 0.6  | service time despite using a small attack bandwidth                                                                                                                                                                                                                                            | 56       |

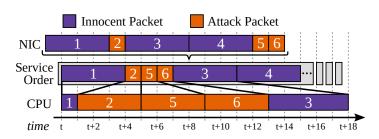

| 3.6  | In order to exploit SJF, the attacker uses minimum-sized packets with a job size (i.e., CPU time) between that of packets 1 and 3. The attack packets (i.e., 2, 5, 6) are scheduled before more expensive ones (3, 4), pushing the system into                                                 |          |

|      | overload and displacing packet 4                                                                                                                                                                                                                                                               | 57       |

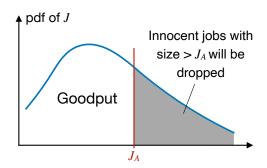

| 3.7  | Optimal choice of adversarial job size $J_A$                                                                                                                                                                                                                                                   | 58       |

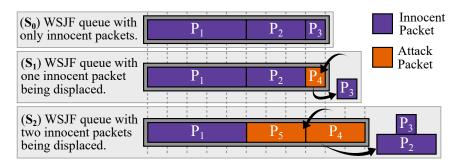

| 3.8  | WSJF service order in steady state                                                                                                                                                                                                                                                             | 60       |

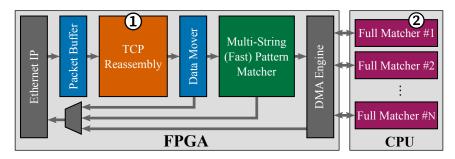

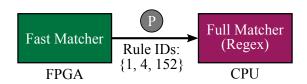

| 3.9  | The simplified Pigasus IDS pipeline.                                                                                                                                                                                                                                                           | 64       |

| 3.10 | Linked-list state for an out-of-order flow.                                                                                                                                                                                                                                                    | 65       |

| 3.11 | Pigasus Full Matching pipeline.                                                                                                                                                                                                                                                                | 65       |

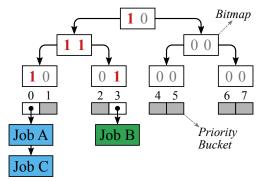

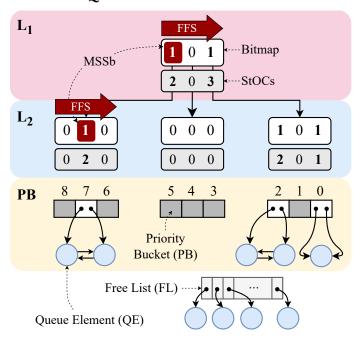

| 3.12 | A Hierarchical FFS Queue implemented using 2-bit bitmaps and height of $h=3$ . A '1' in any bitmap indicates a non-empty priority bucket in the subtree rooted at that node. In order to find the $min$ (or $max$ ) priority bucket, we recursively follow the leftmost (or rightmost) set bit | 68       |

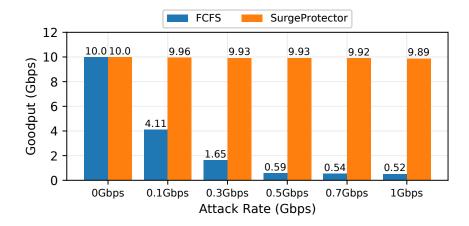

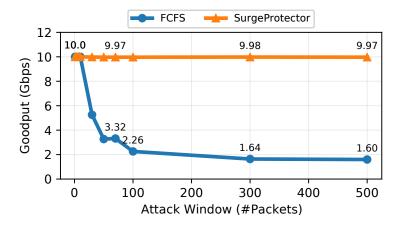

| 3.13 | Goodput of Pigasus' TCP Reassembler under FCFS and SURGEPROTECTOR                                                                                                                                                                                                                              | 69       |

| 3.14 |                                                                                                                                                                                                                                                                                                | 70       |

| 3.15 | Goodput of Pigasus' Full Matcher under FCFS and SURGEPROTECTOR                                                                                                                                                                                                                                 | 70       |

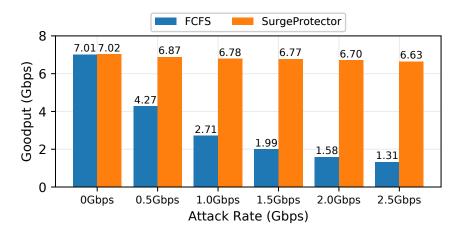

| 3.16 | Simulator pipeline.                                                                                                                                                                                                                                                                            | 71       |

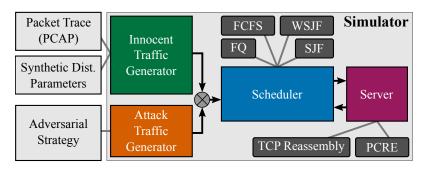

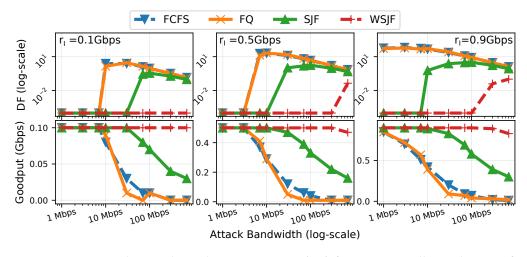

| 3.17 | Goodput and Displacement Factor (DF) for TCP Reassembly. Left to right: Increasing innocent input rate, $r_I$ , from 1 Gbps to 10 Gbps                                                                                                                                                         | 72       |

| 3.18 | Goodput and Displacement Factor (DF) for Pigasus Full Matching. Left to right: Increasing innocent input rate ( $r_I$ ) from 0.1 Gbps to 0.9 Gbps                                                                                                                                              |          |

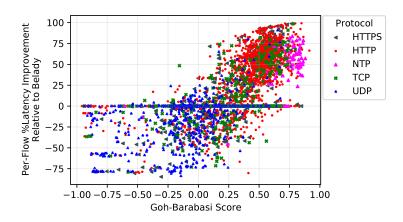

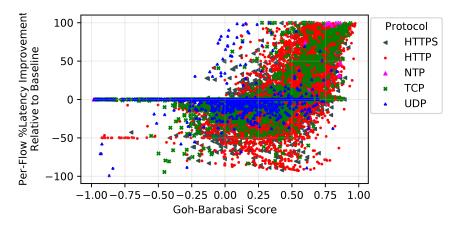

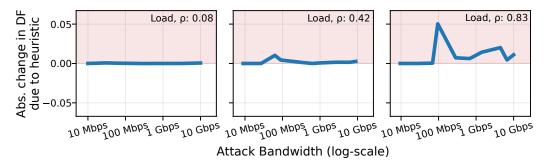

| 3.19 | highlighted in red indicate regions where the heuristic does worse than the baseline.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 73  |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

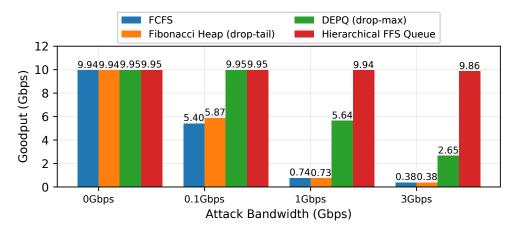

| 3.20 | Goodput for different heap implementations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 74  |

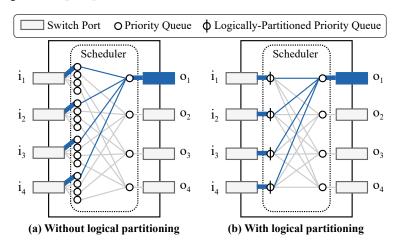

| 4.1  | Scheduler architecture using priority queues without (left), and with (right) support for logical partitioning. In a $k$ -port switch using priority queues without logical partitioning, we need $k^2 + k$ priority queues in order to both implement output queueing $and$ absorb incast traffic from all the ports. Support for logical partitioning reduces the number to $2k$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 81  |

| 4.2  | 2-level BBQ with $w=3$ bit bitmaps. To dequeue the highest-priority element, we recursively perform FFS at each level starting with the root, following the most-significant set bit (MSSb) until we arrive at the required priority bucket                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 85  |

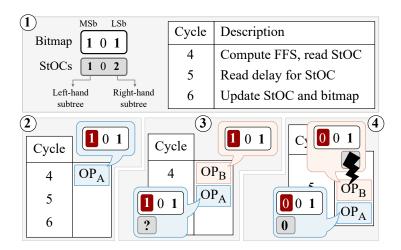

| 4.3  | Non-atomic read-modify-write accesses to bitmaps cause $OP_B$ (the second of two consecutive DEQUEUE-MAX operations) to be incorrectly routed to the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |

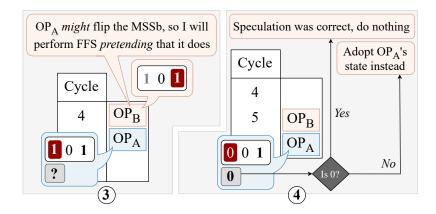

| 4.4  | left-hand subtree.  If there are conflicting operations in the $L_i$ PHRs, operations issued later compute hit indicates are substituted by a substitute of the hitman sub | 91  |

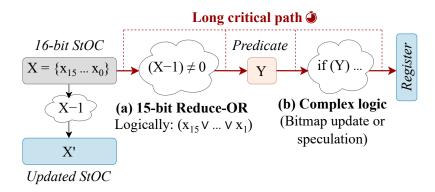

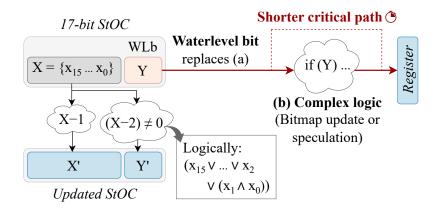

| 4.5  | pute bit indices <i>speculating</i> that earlier operations will change the bitmap Dependency chain involving 16-bit counter logic for a DEQUEUE operation. The critical path comprises of (a) a 15-bit Reduce-OR (to determine whether the StOC becomes 0), chained with (b) more combinational logic (which uses (a) as                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 92  |

|      | a predicate).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 94  |

| 4.6  | The waterlevel bit (WLb) replaces (a), improving $f_{\text{max}}$ by removing the counter operations from the critical path                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 95  |

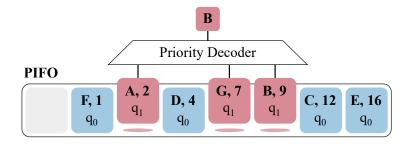

| 4.7  | A single physical PIFO partitioned into 2 logical PIFOs: $q_0$ consisting of 4 elements, and $q_1$ consisting of 3 elements. Available queue memory is fully multi-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | , , |

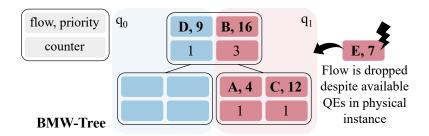

| 4.8  | plexed among the logical PIFOs, resulting in zero fragmentation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 96  |

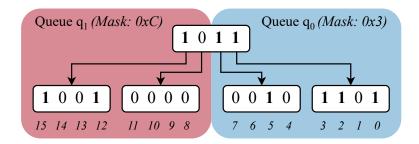

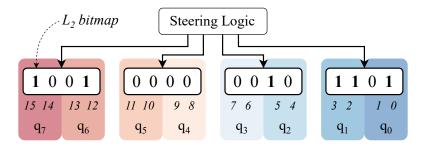

| 4.9  | queue are impossible even if there are available QEs in other subtrees Bitmap tree for a 2-level BBQ with 4-bit bitmaps partitioned into 2 logical BBQs, $q_0$ and $q_1$ . Each logical BBQ is allocated disjoint ranges of 8 priorities. To DEQUEUE from a logical BBQ, we first apply the corresponding $mask$ to the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 97  |

|      | $L_1$ bitmap before performing FFS on it                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 98  |

| 4.10 | Bitmap tree for a 2-level BBQ with 4-bit bitmaps partitioned into 8 logical BBQs. The root $(L_1)$ bitmap no longer adds any value, so we replace it with a <i>steering</i>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |     |

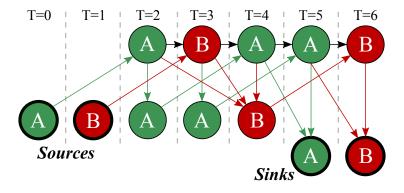

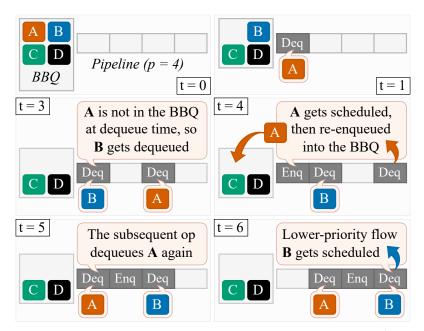

| 4.11 | latency, incorrectly causes a lower-priority flow, B, to be extracted (at $t=3$ )                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     |

| 110  | and scheduled (at $t=6$ )                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     |

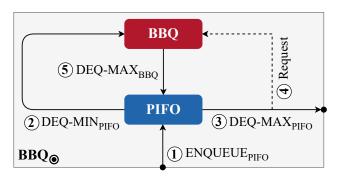

| 4.12 | BBQ $_{\odot}$ design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     |

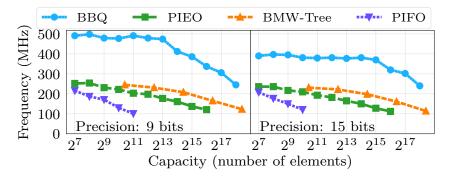

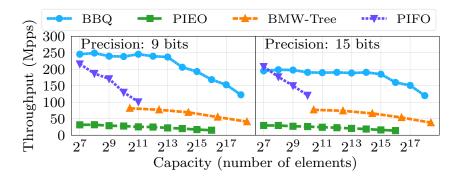

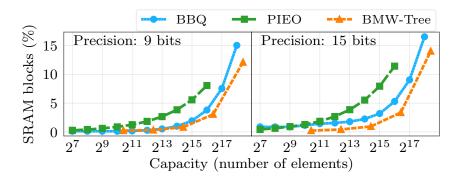

|      | Throughput as we scale the queue capacity                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     |

| 4.15 | ALM utilization as we scale the queue capacity.                                 | 105 |

|------|---------------------------------------------------------------------------------|-----|

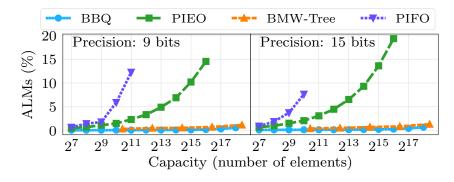

| 4.16 | SRAM block utilization as we scale the queue capacity. PIFO is not included in  |     |

|      | the plot as it does not use SRAM                                                | 106 |

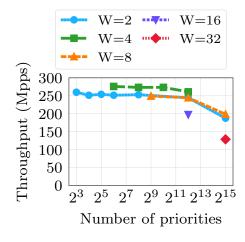

| 4.17 | BBQ throughput as we increase the number of priorities when using different     |     |

|      | bitmap widths (W).                                                              | 107 |

| 4.18 | BBQ throughput as we increase the number of priorities when using different     |     |

|      | number of levels (D).                                                           | 107 |

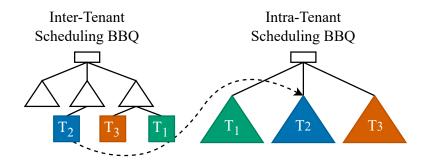

| 4.19 | A two-level hierarchical NIC scheduler using BBQ. The first BBQ schedules traf- |     |

|      | fic across tenants. The second BBQ (which is logically partitioned) is used to  |     |

|      | schedule traffic within each tenant                                             | 109 |

# **List of Tables**

| 2.1 | Average inter-request times (IRT), typical latencies, and $Z$ values seen today        | 10  |

|-----|----------------------------------------------------------------------------------------|-----|

| 2.2 | Empirical bounds on BELATEDLY's error (calculated by comparing the integer             |     |

|     | upper-bound to the relaxed lower-bound)                                                | 27  |

| 2.3 | Overview of implemented online caching algorithms                                      |     |

| 3.1 | Summary of notations used in the model                                                 | 53  |

| 4.1 | Priority Queue operations supported by BBQ                                             | 86  |

| 4.2 | 11-stage hardware pipeline for a 2-level BBQ (without operation coloring) high-        |     |

|     | lighting independent pipeline hazard regions (PHRs). ↓ and ↔ indicate same-            |     |

|     | stage dependencies, which result in more complex combinational logic. In gen-          |     |

|     | eral, a BBQ with $D > 1$ levels entails a pipeline depth of $p = 7 + 4 \times (D - 1)$ |     |

|     | stages                                                                                 | 88  |

| 4.3 | Updated stages $7-10$ showing operation coloring                                       | 93  |

| 4.4 | Chip area for the different designs. BBQ uses little logic, causing its area to be     |     |

|     | primarily determined by SRAM                                                           | 107 |

# Chapter 1

# Introduction

"All models are wrong, but some are useful."

GEORGE E. P. Box

Since the early days of the ENIAC, our ability to engineer complex computer systems has evolved at an astounding pace. Where previously instantiating a service at Internet scale was a matter of innovation, today it is one of simple, formulaic composition: integrating the application with a few elemental *subsystems* (*e.g.*, caches, firewalls, and schedulers) that imbue it with properties such as performance, security, and scalability. But the system itself is only part of the equation; a primary bottleneck in the systems-building process — and one where human ingenuity continues to shine — lies in making the key design and business decisions governing deployment. Which caching algorithms should we use? How much attack mitigation capacity should we pay for? How many elements must the scheduler support?

While these questions appear in different contexts, they share a common epistemological basis: answering them requires us to invoke **models** of how the underlying components behave. Sometimes, the model is *explicit*, based on formal or mathematical reasoning; an archetypal example of this is the *Average Memory Access Time (AMAT)*, an analytical expression we teach in undergraduate computer architecture which posits that improving a cache's hit-rate also reduces its average request latency. Other times, it is *implicit*, *e.g.*, encoded as a practitioner's heuristic or belief that deploying a firewall with higher nominal throughput will improve user experience. Regardless of how they manifest, these models endow us with all of the predictive power that we have and need to make real-world decisions.

However, unsurprisingly, models are not *perfect*. As abstractions, they are necessarily limited in precision both by their form (distilled representations of reality), and their function (being analytically tractable and fitting within the cognitive limits of their designers). Given this fundamental tension between precision and simplicity, the usefulness of a model ultimately depends on *how much* and *how frequently* it is wrong about the details that matter. When the magnitude and frequency of errors grows too large, it results in a problem I call **model incongruity**: material dissonance between the model and the system it is *supposed* to represent.

Model incongruities matter because they disrupt our ability to make the "right" design and business decisions. They might cause a caching algorithm with the highest hit-rate to unexpectedly deliver *worse* latency in the field, or a throughput-optimizing firewall to altogether *starve* traffic under certain workloads. The problem is compounded by their subtlety; unlike traditional bugs which violate easily-checkable correctness criteria, incongruities distort higher-order metrics (*e.g.*, performance, scalability) that are beyond the purview of established testing methodologies and verification tools. Consequently, incongruities remain latent in production systems until they are triggered by a subtle shift in workload, a scaling inflection point, or an adversary who learns how to exploit them.

Over the years, the computer systems community has evolved several adaptations to manage the perennial risk posed by incongruities, from over-provisioning resources to extensive benchmarking as a way of compensating for theoretical blind spots. And while these strategies are effective (perhaps even necessary) in the short term, they only provide temporary, symptomatic relief; as deployment circumstances evolve (e.g., network line-rates go up, or the number of users double), each stopgap must be re-tuned or replaced. In effect, system design has converged to a precarious equilibrium: relying on system models to guide billion-dollar deployment decisions, while quietly dreading the reality that the system is more brittle than it appears. This raises the central question: how can we begin to unequivocally trust our models of computer systems?

In this thesis, we argue that many incongruities observed in practice today are not a fundamental limitation of modeling, but rather artifacts of using the *wrong* models. We exemplify this point using case studies of three ubiquitous network subsystems: caches, packet processors (*e.g.*, firewalls), and packet schedulers. In each case, we show that: (a) fundamental assumptions underpinning contemporary models of network subsystems have drifted far from deployment realities; (b) these assumptions are frequently violated in the field, subverting the operator's expectations about key metrics in highly unexpected ways; and, (c) making modest model refinements not only yields designs with state-of-the-art performance, attack resilience, and scalability, but also enables us to make rigorous mathematical guarantees about the resulting system's behavior which, importantly, also hold in practice.

**Thesis:** Refining classical models of network subsystems (e.g., caches, packet processors, schedulers) to reflect modern deployment contexts yields designs with provably higher performance, greater attack resilience, and improved scalability.

Overall, our findings suggest that a concerted effort towards revamping system models *en masse* will not only improve our short-term understanding of today's deployments, but will also pay long-term dividends in our ability to ultimately *build* better systems in the future.

### 1.1 Why Now?

While model incongruities are as old as modeling itself, three recent trends have exacerbated their prevalence and impact in modern networked systems.

Growing disparity between system complexity and model sophistication. While systems today can be deployed at scales and levels of complexity unimaginable a few decades ago, the models we use to reason about them have not advanced at the same pace. For instance, the analytical and simulation caching models used today remain anchored in abstractions dating back to the 1960s: Bélády's paging model of caching and offline optimal algorithm (1966) continue to serve as the *de facto* benchmark for evaluating modern caching algorithms, and the AMAT expression (1990), which posits that maximizing cache hit-rate is mathematically equivalent to minimizing request latency, still guides deployment decisions in Internet-scale caching. And while the theoretical foundations due to these models have faithfully served many generations of systems, as we will see in §2.1, they are now misaligned with deployment realities. This misalignment is especially problematic in the context of *networked* systems, which are routinely subject to interactions with all classes of Internet-capable users: inquisitive humans, algorithmic bots, and, increasingly, autonomous AI agents. In such settings, it is all the more imperative that our models of system behavior be commensurate with the system itself.

Increasing cost of model predictions being wrong. The early Internet had a single goal: communication. As a result, service providers' concerns were largely centered around whether or not users' data was correctly delivered across the network. In contrast, modern services are evaluated on a much broader set of metrics, many of which are now enshrined in service-level agreements (SLAs). Thanks to SLAs, expectations are commodified, and properties once treated as "best-effort" (e.g., throughput, latency, and availability) have now become contractual obligations. On the one hand, if model predictions are too optimistic and service providers fall short of delivering on them, they risk SLA violations, financial penalties, and reputational damage. Conversely, predictions that are too pessimistic entail wasteful over-provisioning of resources, opportunity costs (losing customers to competitors), or both. In either case, model mispredictions entail high collateral, and the cost only seems to be going up.

Rise of high-stakes failure domains. Finally, the promise of low latency and high throughput has catapulted many "high-stakes" services into the virtual realm (e.g., robotic surgery, autonomous vehicle control); in these domains, even small deviations between predicted and actual behavior can have disproportionate effects. As these applications slowly but surely become mainstream, we can expect the tolerance for modeling error to drop precipitously.

Together, these trends have created conditions in which the limitations of existing models have become both more apparent and costly. We believe that closing the gap between system complexity and model fidelity is therefore an essential prerequisite for building the next generation of reliable, efficient, and secure networked systems.

### 1.2 Summary of Results

This thesis presents three case studies, each corresponding to a real, documented failure mode in the model of a ubiquitous network subsystem. In each case, we demonstrate the implications of incongruity, how modest refinements to the model translate into actionable insights and, ultimately, state-of-the-art system-level improvements realized by leveraging these insights.

**Delayed Hits in Latency-Minimizing Caches** [12]. Textbooks tell us that there are exactly two possible outcomes when an object is requested: a low-latency cache *hit*, or a higher latency cache *miss*. In reality, there is a third potential outcome that the classical caching model missed: a *delayed hit*. Delayed hits occur in high-throughput systems when multiple requests for the same object occur before an outstanding cache miss is resolved. We demonstrated: